超高速0.18μm CMOS復(fù)接器集成電路設(shè)計(jì)

隨著現(xiàn)代通信系統(tǒng)和數(shù)據(jù)傳輸網(wǎng)絡(luò)對(duì)速度與帶寬的需求日益增長,高速復(fù)接器作為實(shí)現(xiàn)多路數(shù)據(jù)流高效整合與傳輸?shù)年P(guān)鍵模塊,其性能至關(guān)重要。采用先進(jìn)的0.18微米互補(bǔ)金屬氧化物半導(dǎo)體工藝進(jìn)行設(shè)計(jì),能夠在功耗、速度與集成度之間取得優(yōu)異的平衡。本文將探討基于0.18μm CMOS工藝的超高速復(fù)接器集成電路設(shè)計(jì)的關(guān)鍵技術(shù)與實(shí)現(xiàn)方案。

一、 設(shè)計(jì)目標(biāo)與挑戰(zhàn)

超高速復(fù)接器的主要設(shè)計(jì)目標(biāo)是在給定工藝下,實(shí)現(xiàn)盡可能高的數(shù)據(jù)吞吐率、低的時(shí)序抖動(dòng)、良好的信號(hào)完整性以及低的功耗。在0.18μm CMOS工藝節(jié)點(diǎn)下,設(shè)計(jì)面臨的核心挑戰(zhàn)包括:

- 速度瓶頸:晶體管的寄生電容和互連線的RC延遲限制了電路的最高工作頻率。

- 信號(hào)完整性:在GHz級(jí)的工作頻率下,傳輸線效應(yīng)、串?dāng)_、電源/地噪聲等問題變得突出。

- 功耗管理:高速切換必然帶來動(dòng)態(tài)功耗的顯著增加,需要進(jìn)行有效的低功耗設(shè)計(jì)。

- 時(shí)鐘分布:為多路選擇器提供低抖動(dòng)、高精度的同步時(shí)鐘是保證性能的關(guān)鍵。

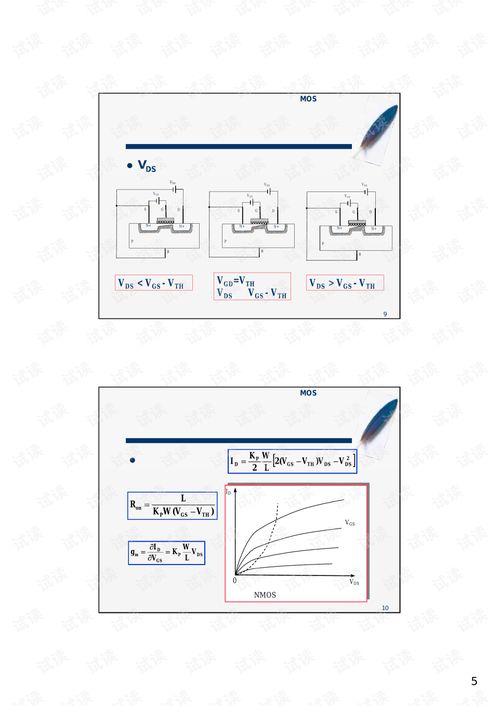

二、 核心電路架構(gòu)選擇

對(duì)于超高速應(yīng)用,常見的復(fù)接器架構(gòu)包括:

- 基于傳輸門的選擇器:結(jié)構(gòu)簡(jiǎn)單,但速度受限于傳輸門的導(dǎo)通電阻和負(fù)載電容。

- 電流模邏輯復(fù)接器:例如采用CML結(jié)構(gòu),具有高速、抗干擾能力強(qiáng)的優(yōu)點(diǎn),但功耗相對(duì)較高,且需要額外的電平轉(zhuǎn)換電路與核心CMOS邏輯接口。

- 基于真單相時(shí)鐘邏輯的樹型結(jié)構(gòu):通過多級(jí)樹狀結(jié)構(gòu)降低每級(jí)負(fù)載,適合超高并行度復(fù)接,但時(shí)鐘設(shè)計(jì)復(fù)雜。

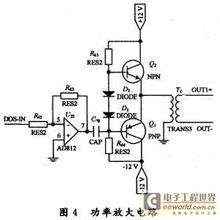

在0.18μm CMOS工藝下,為兼顧速度與功耗,一種高效的方案是采用 “預(yù)充電-求值”邏輯(如多米諾邏輯)與CML輸出級(jí)相結(jié)合的混合架構(gòu)。數(shù)據(jù)選擇通路采用優(yōu)化的多米諾邏輯實(shí)現(xiàn)核心的2選1或4選1單元,以獲得高速度和較低的動(dòng)態(tài)功耗;最終輸出級(jí)采用CML驅(qū)動(dòng)器,以提供穩(wěn)定的高速差分輸出,增強(qiáng)驅(qū)動(dòng)能力和抗噪聲性能。

三、 關(guān)鍵模塊設(shè)計(jì)與優(yōu)化

- 高速選擇單元設(shè)計(jì):

- 采用時(shí)鐘控制的動(dòng)態(tài)邏輯(多米諾邏輯)作為基本選擇單元。通過精心設(shè)計(jì)上拉網(wǎng)絡(luò)和下拉網(wǎng)絡(luò)的晶體管尺寸,優(yōu)化充電和放電路徑,減少關(guān)鍵路徑延遲。

- 引入保持器電路以防止動(dòng)態(tài)節(jié)點(diǎn)在求值階段因漏電導(dǎo)致的邏輯錯(cuò)誤,同時(shí)需謹(jǐn)慎設(shè)計(jì)其尺寸以避免與下拉管競(jìng)爭(zhēng)。

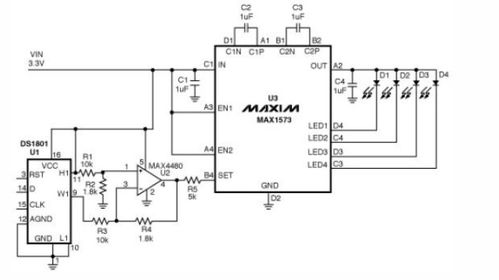

- 時(shí)鐘生成與分布網(wǎng)絡(luò):

- 采用鎖相環(huán)或延遲鎖相環(huán)生成低抖動(dòng)的高速核心時(shí)鐘。

- 設(shè)計(jì)對(duì)稱的H樹或網(wǎng)格狀時(shí)鐘分布網(wǎng)絡(luò),確保時(shí)鐘信號(hào)到達(dá)各個(gè)選擇單元的延時(shí)偏差最小。

- 在時(shí)鐘路徑上插入緩沖器鏈并進(jìn)行尺寸優(yōu)化,以平衡延遲和驅(qū)動(dòng)能力。

- 輸出緩沖器/驅(qū)動(dòng)器設(shè)計(jì):

- 采用CML輸出級(jí)。設(shè)計(jì)定制的尾電流源和負(fù)載電阻,以在滿足輸出擺幅(通常為200-400mV)的前提下,實(shí)現(xiàn)所需的帶寬和功耗指標(biāo)。

- 考慮片外傳輸線阻抗匹配,通常在輸出端集成片上終端電阻(如50Ω)。

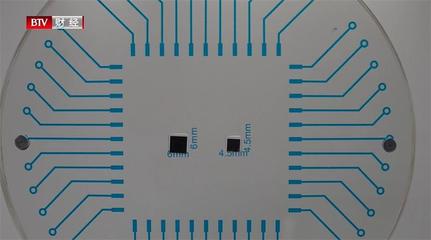

- 布局與版圖考慮:

- 對(duì)稱性:對(duì)差分路徑和關(guān)鍵信號(hào)路徑進(jìn)行嚴(yán)格的對(duì)稱布局,以抵消工藝偏差和降低共模噪聲影響。

- 寄生參數(shù)控制:使用高層金屬(如頂層厚金屬)布線關(guān)鍵高速信號(hào)線,以減小電阻和線間電容;增加線間距以減少串?dāng)_。

- 電源完整性:布置密集的電源和地線網(wǎng)絡(luò),并廣泛使用去耦電容,尤其是在高速電路模塊周圍,為瞬態(tài)電流提供低阻抗回路。

- 靜電防護(hù):所有輸入/輸出焊盤必須集成符合工藝標(biāo)準(zhǔn)的ESD保護(hù)電路,確保芯片可靠性。

四、 設(shè)計(jì)驗(yàn)證與仿真

在設(shè)計(jì)流程中,需進(jìn)行多層次仿真驗(yàn)證:

- 前端仿真:使用電路仿真工具對(duì)晶體管級(jí)電路進(jìn)行直流、瞬態(tài)和AC分析,驗(yàn)證邏輯功能、建立/保持時(shí)間、傳輸延遲及帶寬。

- 后仿:提取包含所有寄生電阻、電容的版圖網(wǎng)表進(jìn)行仿真,這是評(píng)估實(shí)際芯片性能的關(guān)鍵步驟,尤其關(guān)注由寄生效應(yīng)引起的速度下降和信號(hào)畸變。

- 系統(tǒng)級(jí)驗(yàn)證:將復(fù)接器置于完整的收發(fā)鏈路中進(jìn)行仿真,驗(yàn)證其在系統(tǒng)環(huán)境下的性能。

五、

基于0.18μm CMOS工藝設(shè)計(jì)超高速復(fù)接器,需要綜合運(yùn)用先進(jìn)的電路技術(shù)、精心的版圖設(shè)計(jì)和深入的寄生參數(shù)分析。通過采用動(dòng)態(tài)邏輯與電流模邏輯相結(jié)合的混合架構(gòu),并著力優(yōu)化時(shí)鐘網(wǎng)絡(luò)、輸出驅(qū)動(dòng)及電源分布,可以實(shí)現(xiàn)在該工藝節(jié)點(diǎn)下達(dá)到數(shù)Gb/s乃至10Gb/s量級(jí)的數(shù)據(jù)吞吐率。此類設(shè)計(jì)不僅滿足了當(dāng)前高速接口的需求,也為后續(xù)更先進(jìn)工藝下的設(shè)計(jì)積累了寶貴經(jīng)驗(yàn)。隨著工藝向深亞微米發(fā)展,設(shè)計(jì)挑戰(zhàn)將轉(zhuǎn)向更極端的信號(hào)完整性和功耗管理問題。

如若轉(zhuǎn)載,請(qǐng)注明出處:http://m.ivylaser.com.cn/product/3.html

更新時(shí)間:2026-03-21 15:57:29